Memoria d'accesu aleatoriu

Esti artículu o seición necesita referencies qu'apaezan nuna publicación acreitada, como revistes especializaes, monografíes, prensa diaria o páxines d'Internet fiables. |

| |

| Tipu |

type of computer memory or storage (en) |

|---|---|

La memoria d'accesu aleatoriu (Random Access Memory, RAM) utilízase como memoria de trabayu d'ordenadores y otros dispositivos pal sistema operativu, los programes y la mayor parte del software. Na RAM cárguense toles instrucciones qu'executa la unidá central de procesamientu (procesador) y otres unidaes del ordenador, amás de contener los datos que manipolien los distintos programes.

Denominar d'accesu aleatoriu» porque puede lleese o escribir nuna posición de memoria con un tiempu d'espera igual pa cualquier posición, nun siendo necesariu siguir un orde p'aportar (accesu secuencial) a la información de la manera más rápida posible.

Mientres l'encendíu del ordenador, la rutina POST verifica que los módulos de RAM tean coneutaos de manera correuta. Nel casu que nun esistan o nun se detecten los módulos, la mayoría de tarxetes madres emiten una serie de soníos qu'indiquen l'ausencia de memoria principal. Termináu esi procesu, la memoria BIOS puede realizar un test básicu sobre la memoria RAM indicando fallos mayores na mesma.

Historia[editar | editar la fonte]

Unu de los primeros tipos de memoria RAM foi la memoria de nucleu magnéticu, desenvuelta ente 1949 y 1952 y usada en munchos ordenadores hasta'l desenvolvimientu de circuitos integraos a finales de los años 60 y principios de los 70. Esa memoria riquía que cada bit tuviera almacenáu nun toroide de material ferromagnético de dellos milímetros de diámetru, lo que resultaba en dispositivos con una capacidá de memoria bien pequeña. Primero que eso, los ordenadores usaben relés y llinies de retardo de dellos tipos construyíes pa implementar les funciones de memoria principal con o ensin accesu aleatoriu.

En 1969 fueron llanzaes una de les primeres memories RAM basaes en semiconductores de siliciu per parte d'Intel col integráu 3101 de 64 bits de memoria y pal siguiente añu presentóse una memoria DRAM de 1024 bytes, referencia 1103 que se constituyó nun finxu, yá que foi la primera en ser comercializada con ésitu, lo que significó'l principiu del fin pa les memories de nucleu magnéticu. En comparanza colos integraos de memoria DRAM actuales, la 1103 ye primitiva en dellos aspeutos, pero tenía un desempeñu mayor que la memoria de nucleos.

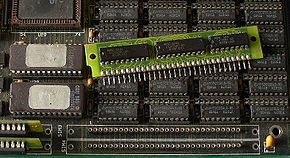

En 1973 presentóse una innovación que dexó otra miniaturización y convirtióse n'estándar pa les memories DRAM: la multiplexación en tiempu de la direiciones de memoria. MOSTEK llanzó la referencia MK4096 de 4096 bytes nun barafuste de 16 pines,[1] mientres los sos competidores fabricar nel barafuste DIP de 22 pines. L'esquema de direccionamientu[2] convertir nun estándar de facto por cuenta de la gran popularidá que llogró esta referencia de DRAM. Pa finales de los 70 los integraos yeren usaos na mayoría d'ordenadores nuevos, soldábense direutamente a les plaques base o s'instalaben en zócalos, de manera qu'ocupaben una área estensa de circuitu impresu. Col tiempu fíxose obviu que la instalación de RAM sobre l'impresu principal, torgaba la miniaturización , entós escurriéronse los primeros módulos de memoria como'l SIPP, aprovechando les ventayes de la construcción modular. El formatu SIMM foi una meyora al anterior, esaniciando los pines metálicos y dexando unes árees de cobre n'unu de los cantos del impresu, bien similares a los de les tarxetes d'espansión, de fechu los módulos SIPP y los primeres SIMM tienen la mesma distribución de pines.

A finales de los 80 l'aumentu na velocidá de los procesadores y l'aumentu nel anchu de banda riquíu, dexaron arrezagaes a les memories DRAM col esquema orixinal MOSTEK, de manera que se realizaron una serie de meyores nel direccionamientu como les siguientes:

FPM RAM[editar | editar la fonte]

Fast Page Mode RAM (FPM-RAM) foi inspiráu en téuniques como'l Burst Mode usáu en procesadores como'l Intel 486.[3] Enllantóse una manera direccionamientu nel que'l controlador de memoria unvia una sola direición y recibe a cambéu esa y delles consecutives ensin necesidá de xenerar toles direiciones. Esto supón un aforru de tiempos una y bones ciertes operaciones son repetitives cuando se desea aportar a munches posiciones consecutives. Funciona como si deseyáramos visitar toles cases nuna cai: dempués de la primer vegada nun sería necesariu dicir el númberu de la cai namái siguir la mesma. Fabricar con tiempos d'accesu de 70 ó 60 ns y fueron bien populares en sistemes basaos nel 486 y los primeres Pentium.

EDO RAM[editar | editar la fonte]

Extended Data Output RAM (EDO-RAM) foi llanzada al mercáu en 1994 y con tiempos d'accesos de 40 o 30 ns supónía una ameyora sobre FPM, la so antecesora. La EDO, tamién ye capaz d'unviar direiciones allegantes pero direcciona la columna que va utilizar ente que se llee la información de la columna anterior, dando como resultáu una eliminación d'estaos d'espera, calteniendo activu'l búfer de salida hasta qu'empieza'l próximu ciclu de llectura.

BEDO RAM[editar | editar la fonte]

Burst Extended Data Output RAM (BEDO-RAM) foi la evolución de la EDO-RAM y competidora de la SDRAM, foi presentada en 1997. Yera un tipu de memoria qu'usaba xeneradores internos de direiciones y aportaba a más d'una posición de memoria en cada ciclu de reló, de manera que llograba un 50 % de beneficios, meyor que la EDO. Nunca salió al mercáu, yá que Intel y otros fabricantes decidir por esquemes de memoria sincrónicos que magar teníen enforma del direccionamientu MOSTEK, amiesten funcionalidades distintes como señales de reló.

Tipos de RAM[editar | editar la fonte]

Los dos formes principales de RAM moderna son:

- SRAM (Static Random Access Memory), RAM estática, memoria estática d'accesu aleatoriu.

- volátiles.

- non volátiles:

- NVRAM (non-volatile random access memory), memoria d'accesu aleatoriu non volátil

- MRAM (magnetoresistive random-access memory), memoria d'accesu aleatoriu magnetorresistiva o magnética #

DRAM (Dynamic Random Access Memory), RAM dinámica, memoria dinámica d'accesu aleatoriu.

- DRAM Asincrónica (Asynchronous Dynamic Random Access Memory, memoria d'accesu aleatoriu dinámica asincrónica)

- FPM RAM (Fast Page Mode RAM)

- EDO RAM (Extended Data Output RAM)

- SDRAM (Synchronous Dynamic Random-Access Memory, memoria d'accesu aleatoriu dinámica sincrónica)

- Rambus:

- SDR SDRAM (Single Data Rate Synchronous Dynamic Random-Access Memory, SDRAM de tasa de datos simple)

- DDR SDRAM (Double Data Rate Synchronous Dynamic Random-Access Memory, SDRAM de tasa de datos doble)

- DDR2 SDRAM (Double Data Rate type two SDRAM, SDRAM de tasa de datos doble de tipo dos)

- DDR3 SDRAM (Double Data Rate type three SDRAM, SDRAM de tasa de datos doble de tipu trés)

- DDR4 SDRAM (Double Data Rate type four SDRAM, SDRAM de tasa de datos doble de tipu cuatro)

- DRAM Asincrónica (Asynchronous Dynamic Random Access Memory, memoria d'accesu aleatoriu dinámica asincrónica)

Nomenclatura[editar | editar la fonte]

La espresión memoria RAM utilízase frecuentemente pa describir a los módulos de memoria utilizaos nes ordenadores personales y servidores.

La RAM ye solo una variedá de la memoria d'accesu aleatoriu: les ROM, memories Flash, caxé (SRAM), los rexistros en procesadores y otres unidaes de procesamientu tamién tienen la cualidá de presentar retardos d'accesu iguales pa cualquier posición.

Los módulos de RAM son la presentación comercial d'esti tipu de memoria, que se compón de circuitos integraos soldaos sobre un circuitu impresu independiente, n'otros dispositivos como les consoles de videoxuegos, la RAM va soldada direutamente sobre la placa principal.

Módulos de RAM[editar | editar la fonte]

Los módulos de RAM son tarxetes o plaques de circuitu impresu que tienen soldaos chips de memoria DRAM, por una o dambes cares.

La implementación DRAM basar nuna topoloxía de circuitu llétricu que dexa algamar densidaes altes de memoria por cantidá de transistores, llogrando integraos de cientos o miles de megabits. Amás de DRAM, los módulos tienen un integráu que dexen la identificación de los mesmos ante l'ordenador per mediu del protocolu de comunicación Serial Presence Detect (SPD).

La conexón colos demás componentes realizar por mediu d'una área de pines n'unu de los filos del circuitu impresu, que dexen que'l módulu al ser instaláu nun zócalo o ranura apropiada de la placa base, tenga bon contautu llétricu con el controladores de memoria y les fontes d'alimentación.

La necesidá de faer intercambiable los módulos, y d'utilizar integraos de distintos fabricantes, condució al establecimientu d'estándares de la industria como los Joint Electron Device Engineering Council (JEDEC).

- Paquete DIP (Dual In-line Package, paquete de pines en llinia doble).

- Paquete SIPP (Single In-line Pin Package, paquete de pines en llinia simple): fueron los primeros módulos comerciales de memoria, de formatu propietariu, esto ye, nun había un estándar ente distintes marques.

- Módulos RIMM (Rambus In-line Memory Module, módulu de memoria en-llinia rambus): Fueron otros módulos propietarios bastante conocíos, escurríos pola empresa RAMBUS.

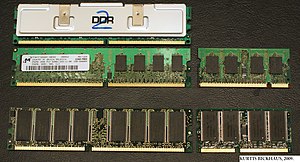

- Módulos SIMM (Single In-line Memory Module, módulu de memoria en llinia simple): formatu usáu n'ordenadores antiguos. Teníen un bus de datos de 16 ó 32 bits.

- Módulos DIMM (Dual In-line Memory Module, módulu de memoria en llinia dual): usáu n'ordenadores d'escritoriu. Carauterizar por tener un bus de datos de 64 bits.

- Módulos SO-DIMM (Small Outline DIMM): usáu n'ordenadores portátiles. Formatu miniaturizado de DIMM.

- Módulos FB-DIMM (Fully-Buffered Dual Inline Memory Module): usáu en servidores.

Teunoloxíes de memoria[editar | editar la fonte]

La teunoloxía de memoria actual usa una señal de sincronización pa realizar les funciones de llectura/escritura de manera que siempres ta sincronizada con un reló del bus de memoria, a diferencia de les antigües memories FPM y EDO que yeren asíncronas.

Tola industria decantar poles teunoloxíes síncronas, porque dexen construyir integraos que funcionen a una frecuencia cimera a 66 MHz.

Tipos de DIMM según la so cantidá de contactos o pines:

| Cantidá de pines | Tipos de DIMM | Usaos por: | Observaciones |

|---|---|---|---|

| 072 | SO-DIMM | FPM-DRAM y EDO-DRAM | (non el mesmu qu'un 72-pin SIMM) |

| 100 | DIMM | printer SDRAM | |

| 144 | SO-DIMM | SDR SDRAM | |

| 168 | DIMM | SDR SDRAM | (menos frecuente pa FPM/EDO DRAM n'árees de trabayu y/o servidores) |

| 172 | Micro-DIMM | DDR SDRAM | |

| 184 | DIMM | DDR SDRAM | |

| 200 | SO-DIMM | DDR SDRAM y DDR2 SDRAM | |

| 204 | SO-DIMM | DDR3 SDRAM | |

| 240 | DIMM | DDR2 SDRAM, DDR3 SDRAM y Fully Buffered DIMM (FB-DIMM) DRAM | |

| 244 | Mini-DIMM | DDR2 SDRAM |

SDR SDRAM[editar | editar la fonte]

Memoria síncrona, con tiempos d'accesu d'ente 25 y 10 ns y que se presenten en módulos DIMM de 168 contactos. Foi utilizada nos Pentium II y nos Pentium III , según nos AMD K6, AMD Athlon K7 y Duron. Ta bien estendida la creencia de que se llama SDRAM a seques, y que la denominación SDR SDRAM ye pa estremala de la memoria DDR, pero nun ye asina, a cencielles estendióse bien rápido la denominación incorreuta. El nome correutu ye SDR SDRAM yá que ambes (tantu la SDR como la DDR) son memories síncronas dinámiques. Los tipos disponibles son:

- PC66: SDR SDRAM, funciona a un máx de 66,6 MHz.

- PC100: SDR SDRAM, funciona a un máx de 100 MHz.

- PC133: SDR SDRAM, funciona a un máx de 133,3 MHz.

RDRAM[editar | editar la fonte]

Presentar en módulos RIMM de 184 contactos. Foi utilizada nos Pentium 4 . Yera la memoria más rápida nel so tiempu, pero pol so eleváu costu foi rápido camudada pola económica DDR. Los tipos disponibles son:

- PC600: RIMM RDRAM, funciona a un máximu de 300 MHz.

- PC700: RIMM RDRAM, funciona a un máximu de 350 MHz.

- PC800: RIMM RDRAM, funciona a un máximu de 400 MHz.

- PC1066: RIMM RDRAM, funciona a un máximu de 533 MHz.

- PC1200: RIMN RDRAM, funciona a un máximu de 600 MHz.

DDR SDRAM[editar | editar la fonte]

Memoria síncrona, unvia los datos dos veces per cada ciclu de reló. D'esta miente trabaya al doble de velocidá del bus del sistema, ensin necesidá d'aumentar la frecuencia de reló. Presentar en módulos DIMM de 184 contactos nel casu d'ordenador d'escritoriu y en módulos de 144 contactos pa los ordenadores portátiles.

La nomenclatura utilizada pa definir a los módulos de memoria de tipu DDR (esto inclúi a los formatos DDR2, DDR3 y DDR4) ye la siguiente: DDRx-yyyy PCx-zzzz; onde x representa a la xeneración DDR en cuestión; yyyy la frecuencia aparente o efectiva, en Megaciclos per segundu (MHz); y zzzz la máxima tasa de tresferencia de datos per segundu, en Megabytes, que puede llograse ente'l módulu de memoria y el controlador de memoria. La tasa de tresferencia depende de dos factores, l'anchu de bus de datos (polo xeneral 64 bits) y la frecuencia aparente o efectiva de trabayu. La fórmula que s'utiliza pa calcular la máxima tasa de tresferencia per segundu ente'l módulu de memoria y el so controlador, ye la siguiente:

Tasa de tresferencia en MB/s = (Frecuencia DDR efectiva) x (64 bits / 8 bits por cada byte)[4]

Por casu:

1 GB DDR-400 PC-3200: Representa un módulu de 1 GB (Gigabyte) de tipu DDR; con frecuencia aparente o efectiva de trabayu de 400 MHz; y una tasa de tresferencia de datos máxima de 3200 MB/s.

4 GB DDR3-2133 PC3-17000: Representa un módulu de 4 GB de tipu DDR3; frecuencia aparente o efectiva de trabayu de 2133 MHz; y una tasa de tresferencia de datos máxima de 17000 MB/s.

Los tipos disponibles son:

- PC1600 o DDR 200: funciona a un máx de 200 MHz.

- PC2100 o DDR 266: funciona a un máx de 266,6 MHz.

- PC2700 o DDR 333: funciona a un máx de 333,3 MHz.

- PC3200 o DDR 400: funciona a un máx de 400 MHz.

- PC4500 o DDR 500: funciona a una máx de 500 MHz.

DDR2 SDRAM[editar | editar la fonte]

Les memories DDR 2 son una meyora de les memories DDR (Double Data Rate), que dexen que los búferes d'entrada salida trabayen al doble de la frecuencia del nucleu, dexando que mientres cada ciclu de reló realicen cuatro tresferencies. Presentar en módulos DIMM de 240 contactos. Los tipos disponibles son:

- PC2-3200 o DDR2-400: funciona a un máx de 400 MHz.

- PC2-4200 o DDR2-533: funciona a un máx de 533,3 MHz.

- PC2-5300 o DDR2-667: funciona a un máx de 666,6 MHz.

- PC2-6400 o DDR2-800: funciona a un máx de 800 MHz.

- PC2-8600 o DDR2-1066: funciona a un máx de 1066,6 MHz.

- PC2-9000 o DDR2-1200: funciona a un máx de 1200 MHz.

DDR3 SDRAM[editar | editar la fonte]

Les memories DDR 3 son una meyora de les memories DDR 2, apurren significantes meyores nel rendimientu en niveles de baxu voltaxe, lo que lleva consigo un amenorgamientu del gastu global de consumu. Los módulos DIMM DDR 3 tienen 240 pines, el mesmu númberu que DDR 2; sicasí, los DIMMs son físicamente incompatibles, por cuenta de un allugamientu distintu de la mozqueta. Los tipos disponibles son:

- PC3-6400 o DDR3-800: funciona a un máx de 800 MHz.

- PC3-8500 o DDR3-1066: funciona a un máx de 1066,6 MHz.

- PC3-10600 o DDR3-1333: funciona a un máx de 1333,3 MHz.

- PC3-12800 o DDR3-1600: funciona a un máx de 1600 MHz.

- PC3-14900 o DDR3-1866: funciona a un máx de 1866,6 MHz.

- PC3-17000 o DDR3-2133: funciona a un máx de 2133,3 MHz.

- PC3-19200 o DDR3-2400: funciona a un máx de 2400 MHz.

- PC3-21300 o DDR3-2666: funciona a un máx de 2666,6 MHz.

DDR4 SDRAM[editar | editar la fonte]

- PC4-1600 o DDR4-1600: funciona a un máx de 1600 MHz.

- PC4-1866 o DDR4-1866: funciona a un máx de 1866,6 MHz.

- PC4-17000 o DDR4-2133: funciona a un máx de 2133,3 MHz.

- PC4-19200 o DDR4-2400: funciona a un máx de 2400 MHz.

- PC4-25600 o DDR4-2666: funciona a un máx de 2666,6 MHz.

Rellación col restu del sistema[editar | editar la fonte]

Dientro de la xerarquía de memoria, la RAM atopar nun nivel dempués de los rexistros del procesador y de los caxés tocantes a velocidá.

Los módulos de RAM conéctense llétricamente a un controlador de memoria que xestiona señalar entrantes y salientes de los integraos DRAM. Les señales son de tres tipos: direccionamientu, datos y señales de control. Nel módulu de memoria eses señales tán estremaes en dos buses y un conxuntu misceláneo de llinies de control y alimentación. Ente toes formen el bus de memoria que coneuta la RAM col so controlador:

- Bus de datos: son les llinies que lleven información ente los integraos y el controlador. Polo xeneral, tán arrexuntaos en octetos siendo de 8, 16, 32 y 64 bits, cantidá que tien d'igualar l'anchu del bus de datos del procesador. Nel pasáu, dellos formatos de módulu, nun teníen un anchu de bus igual al del procesador. Nesi casu había que montar módulos en pares o en situaciones estremes, d'a 4 módulos, pa completar lo que se denominaba bancu de memoria, d'otra miente el sistema nun funcionar. Esa foi la principal razón p'aumentar el númberu de pines nos módulos, igualando al anchu de bus de procesadores como'l Pentium a 64 bits, a principios de los años 1990.

- Bus de direiciones: ye un bus nel cual asítiense les direiciones de memoria a les que se riquir aportar. Nun ye igual al bus de direiciones del restu del sistema, yá que ta multiplexado de manera que la direición unviar en dos etapes. Pa ello, el controlador realiza temporizaciones y usa les llinies de control. En cada estándar de módulu establezse un tamañu máximu en bits d'esti bus, estableciendo una llende teórica de la capacidá máxima por módulu.

- Señales misceláneas: ente les que tán les de l'alimentación (Vdd, Vss) que s'encarguen d'apurrir potencia a los integraos. Tán les llinies de comunicación pal integráu de presencia (Serial Presence Detect) que sirve pa identificar cada módulu. Tán les llinies de control ente les que s'atopen les llamaes RAS (Row Address Strobe) y CAS (Column Address Strobe) que controlen el bus de direiciones, d'últimes tán les señales de reló nes memories sincróniques SDRAM.

Dellos controladores de memoria en sistemes como PC y servidores atópense enfiñíos nel llamáu ponte norte (North Bridge) de la placa base. Otros sistemes inclúin el controlador dientro del mesmu procesador (nel casu de los procesadores dende AMD Athlon 64 y Intel Core i7 y posteriores). Na mayoría de los casos el tipu de memoria que puede remanar el sistema ta llindáu polos sockets pa RAM instalaos na placa base, a pesar que'l controladores de memoria en munchos casos son capaces de conectase con teunoloxíes de memoria distintes.

Una carauterística especial de dellos controladores de memoria, ye'l manexu de la teunoloxía canal doble o doble canal (Dual Channel), onde'l controlador remana bancos de memoria de 128 bits, siendo capaz d'apurrir los datos de manera entrepolada, optando por unu o otra canal, amenorgando les llatencies vistes pol procesador. La meyora nel desempeñu ye variable y depende de la configuración y usu del equipu. Esta carauterística hai promovíu el cambéu de los controladores de memoria, resultando na apaición de nuevos chipsets (la serie 865 y 875 d'Intel) o de nuevos zócalos de procesador nos AMD (el 939 con canal doble , reemplazo'l 754 de canal senciella). Los equipos de games media y alta polo xeneral fabríquense basaos en chipsets o zócalos que soporten doble canal o superior, como nel casu del zócalo (socket) 1366 d'Intel, qu'usaba una triple canal de memoria, o'l so nuevu LGA 2011 qu'usa cuádruple canal.

Detección y correición d'errores[editar | editar la fonte]

Esisten dos clases d'errores nos sistemes de memoria, les falles (Hard fails) que son daños nel hardware y los errores (soft errors) provocaos por causes casuales. Los primeres son relativamente fáciles de detectar (en delles condiciones el diagnósticu ye equivocáu), los segundos al ser resultáu d'eventos aleatorios, son más difíciles de topar. Na actualidá la confiabilidad de les memories RAM frente a los errores, ye abondo alta como para nun realizar verificación sobre los datos almacenaos, a lo menos p'aplicaciones d'oficina y caseres. Nos usos más críticos, aplíquense téuniques de correición y detección d'errores basaes en distintes estratexes:

- La téunica del bit de paridá consiste en guardar un bit adicional por cada byte de datos y na llectura comprueba si'l númberu d'unos ye par (“paridá par”) o impar (“paridá impar”), detectándose asina l'error.

- Una téunica meyor ye la qu'usa “códigu de autochequeo y autocorreutor” (error-correcting code, ECC), que dexa detectar errores de 1 a 4 bits y correxir errores qu'afecten a un solu bit. Esta téunica úsase namái en sistemes que riquen alta fiabilidá.

Polo xeneral, los sistemes con cualquier tipu de proteición contra errores tien un costu más altu, y sufren de pequeñes penalizaciones en desempeñu, con al respective de los sistemes ensin proteición. Pa tener un sistema con ECC o paridá, el chipset y les memories tienen de tener soporte pa eses teunoloxíes. La mayoría de plaques base nun tener dichu soporte.

Pa los fallos de memoria pueden utilizase ferramientes de software especializaes que realicen pruebes sobre los módulos de memoria RAM. Ente estos programes unu de los más conocíos ye l'aplicación Memtest86+ que detecta fallos de memoria.

RAM rexistrada[editar | editar la fonte]

Ye un tipu de módulu usáu frecuentemente en servidores, tien circuitos integraos que s'encarguen de repitir les señales de control y direiciones: les señales de reló son reconstruyíes con ayuda del PLL que ta allugáu nel módulu mesmu. Les señales de datos coneutar de la mesma forma que nos módulos ensin rexistrar: de manera direuta ente los integraos de memoria y el controlador. Los sistemes con memoria rexistrada dexen coneutar más módulos de memoria y de una capacidá más alta, ensin qu'haya perturbaciones nes señales del controlador de memoria, dexando'l manexu de grandes cantidaes de memoria RAM. Ente les desventaxes de los sistemes de memoria rexistrada tán el fechu de que s'amiesta un ciclu de retardo pa cada solicitú d'accesu a una posición non consecutiva y un preciu más altu que los módulos ensin rexistrar. La memoria rexistrada ye incompatible con el controladores de memoria que nun soporten la manera rexistrada, a pesar de que pueden instalase físicamente nel zócalo. Pueden reconocese visualmente porque tienen un integráu medianu, cerca del centru xeométricu del circuitu impresu, amás de qu'estos módulos suelen ser daqué más altos.[5]

Mientres l'añu 2006 delles marques llanzaron al mercáu sistemes con memoria FB-DIMM que nel so momentu pensáronse como los socesores de la memoria rexistrada, pero abandonó esa teunoloxía en 2007 yá que ufiertaba poques ventayes sobre'l diseñu tradicional de memoria rexistrada y los nuevos modelos con memoria DDR3.[6]

Ver tamién[editar | editar la fonte]

- Accesu aleatoriu

- Circuitu impresu

- Circuitu integráu

- Doble canal

- DRAM

- Joint Electron Device Engineering Council

- Memoria (informática)

- Memoria de solo llectura

- Memoria FRAM

- Memoria gráfica d'accesu aleatoriu

- Memoria principal

- Memoria volátil

- Ranura d'espansión

- RDRAM

- Serial Presence Detect

- SRAM

- Teunoloxía de montaxe superficial

- Zócalo (electrónica)

Referencies[editar | editar la fonte]

- ↑ «Mostek Firsts». Archiváu dende l'orixinal, el 12 de xineru de 2012. Consultáu'l 2009.

- ↑ «Datasheet & Application Note Database, PDF, Circuits, Datasheets / Datasheet Archive».

- ↑ «mio_m0HPJ/is_/ai_11405923 The HP Vectra 486 memory controller / Hewlett-Packard Journal /Find Articles at BNET». Consultáu'l 2009.

- ↑ «memoria-de-una-ordenador Cómo funciona la memoria d'un ordenador».

- ↑ https://web.archive.org/web/20120310085510/http://download.micron.com/pdf/datasheets/modules/ddr2/HTJ_S36C512_1Gx72.pdf

- ↑ http://www.theinquirer.net/inquirer/news/1014319/fb-dimm-dead-rddr3-king