Biestable

R3, R4 = 10 kΩ

Un biestable (flip-flop n'inglés), ye un multivibrador capaz de permanecer n'unu de dos estaos posibles mientres un tiempu indefiníu n'ausencia de perturbaciones.[1] Esta carauterística ye llargamente utilizada en electrónica dixital para memorizar información. El pasu d'un estáu a otru realízase variando les sos entraes. Dependiendo del tipu de felicidaes entraes los biestables estremar en:

- Asíncronos: solamente tienen entraes de control. El más emplegáu ye'l biestable RS.

- Síncronos: amás de les entraes de control tien una entrada de sincronismu o de reló.

Si les entraes de control dependen de la de sincronismu denominar síncronas y en casu contrariu asíncronas. Polo xeneral, les entraes de control asíncronas prevalecen sobre les síncronas.

La entrada de sincronismu puede ser activada por nivel (alto o baxu) o por lladral (de xubida o de baxada). Dientro de los biestables síncronos activaos por nivel tán los tipos RS y D, y dientro de los activos por lladrales los tipos JK, T y D.

Los biestables síncronos activos per lladral (flip-flop) crear pa esaniciar los defectos de los latches (biestables asíncronos o sincronizaos por nivel).

Biestable RS

[editar | editar la fonte]Descripción

Dispositivu d'almacenamientu temporal de 2 estaos (alto y baxu), que les sos entraes principales dexen al ser activaes:

- R: el borráu (reset n'inglés), puesta a 0 ó nivel baxu de la salida.

- S: el grabáu (set n'inglés), puesta a 1 ó nivel altu de la salida

Si nun s'activa nenguna de les entraes, el biestable permanez nel estáu que tenía tres la última operación de borráu o grabáu. En nengún casu tendríen d'activase dambes entraes al empar, una y bones esto provoca que les salíes direuta (Q) y negada (Q') queden col mesmu valor: a baxu, si'l flip-flop ta construyíu con puertes NOR, o a altu, si ta construyíu con puertes NAND. El problema de que dambes salíes queden al mesmu estáu ta en qu'al desactivar dambes entraes non podrá determinase l'estáu nel que quedaría la salida. Por eso, nes tables de verdá, l'activación de dambes entraes contémplase como caso non deseyáu (N. D.).

Biestable RS (Set Reset) asíncrono

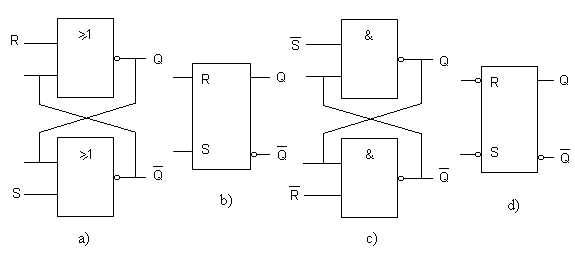

[editar | editar la fonte]Namái tien les entraes R y S. Compónse internamente de dos puertes lóxiques NAND o NOR, según amuésase na siguiente figura:

| R | S | Q (NOR) | Q (NAND) | ||||

|---|---|---|---|---|---|---|---|

0 |

0

|

q

|

N. D.

| ||||

0 |

1

|

1

|

0

| ||||

1 |

0

|

0

|

1

| ||||

1 |

1

|

N. D.

|

q

| ||||

| N. D.= Estáu ensin deseyar q= Estáu de memoria | |||||||

Biestable RS (Set Reset) síncrono

[editar | editar la fonte]Amás de les entraes R y S, tien una entrada C de sincronismu que la so misión ye la de dexar o non el cambéu d'estáu del biestable. Na siguiente figura amuésase un exemplu d'un biestable síncrono a partir d'una asíncrona, xunto col so esquema normalizáu:

La so tabla de verdá ye la siguiente:

| C | R | S | Q (NOR) |

|---|---|---|---|

0 |

X |

X

|

q

|

1 |

0 |

0

|

q

|

1 |

0 |

1

|

1

|

1 |

1 |

0

|

0

|

1 |

1 |

1

|

N. D.

|

| X=nun importa | |||

Biestable D (Data o Delay)

[editar | editar la fonte]El flip-flop D resulta bien útil cuando se precisa almacenar un únicu bit de datos (1 o 0). Si añade un inversor a un flip-flop S-R llogramos un flip-flop D básicu. El funcionamientu d'un dispositivu activáu pol lladral negativu ye, poques gracies, idénticu, sacante que'l disparu tien llugar nel lladral de baxada del impulsu del reló. Recuerde que Q sigue a D en cada lladral del impulsu de reló.

Pa ello, el dispositivu d'almacenamientu temporal ye de dos estaos (alto y baxu), que la so salida adquier el valor de la entrada D cuando s'activa la entrada de sincronismu, C. En función de la manera d'activación de felicidá entrada de sincronismu, esisten dos tipos:

- Activu per nivel (alto o baxu), tamién denomináu rexistru o cerrojo (latch n'inglés).

- Activu per lladral (de xubida o de baxada).

La ecuación carauterística del biestable D que describe'l so comportamientu ye:

y el so tabla de verdá:

| D | Q | Qsiguiente |

|---|---|---|

| 0 | X | 0

|

| 1 | X | 1

|

| X=nun importa | ||

Esta báscula puede trate como una primitiva llinia de retardo o una retención d'orde cero (zero order hold n'inglés), una y bones los datos que s'introducen, llograr na salida un ciclu de reló dempués. Esta carauterística ye aprovechada pa sintetizar funciones de procesamientu dixital de señales (DSP n'inglés) por aciu la Tresformaes de señales tresformada Z.

Exemplu: 74LS74

Biestable T (Toggle)

[editar | editar la fonte]Dispositivu d'almacenamientu temporal de 2 estaos (alto y baxu). El biestable T camuda d'estáu ("toggle" n'inglés) cada vez que la entrada de sincronismu o de reló dispárase mientres la entrada T ta a nivel altu. Si la entrada T ta a nivel baxu, el biestable retién el nivel previu. Puede llograse al xunir les entraes de control d'un biestable JK, unión que se correspuende a la entrada T. Nun tán disponibles comercialmente.

La ecuación carauterística del biestable T que describe'l so comportamientu ye:

y la tabla de verdá:

| T | Q | Qsiguiente |

|---|---|---|

| 0 | 0 | 0

|

| 0 | 1 | 1

|

| 1 | 0 | 1

|

| 1 | 1 | 0

|

Biestable JK

[editar | editar la fonte]Ye versátil y ye unu de los tipos de flip-flop más usaos. El so funcionamientu ye idénticu al del flip-flop S-R nes condiciones SET, RESET y de permanencia d'estáu. La diferencia ta en que'l flip-flop J-K nun tien condiciones non válides como asocede nel S-R.

Esti dispositivu d'almacenamientu ye temporal que s'atopa dos estaos (alto y baxu), que les sos entraes principales, J y K, a les que debe'l nome, dexen al ser activaes:

- J: El grabáu (set n'inglés), puesta a 1 ó nivel altu de la salida.

- K: El borráu (reset n'inglés), puesta a 0 ó nivel baxu de la salida.

Si nun s'activa nenguna de les entraes, el biestable permanez nel estáu que tenía tres la última operación de borráu o grabáu. A diferencia del biestable RS, nel casu d'activase dambes entraes al empar, la salida va adquirir l'estáu contrariu al que tenía.

La ecuación carauterística del biestable JK que describe'l so comportamientu ye:

Y el so tabla de verdá ye:

| J | K | Q | Qsiguiente |

|---|---|---|---|

| 0 | 0 | 0 | 0

|

| 0 | 0 | 1 | 1

|

| 0 | 1 | X | 0

|

| 1 | 0 | X | 1

|

| 1 | 1 | 0 | 1

|

| 1 | 1 | 1 | 0

|

| X=nun importa | |||

Una forma más compacta de la tabla de verdá ye (Q representa l'estáu siguiente de la salida nel próximu lladral de reló y q l'estáu actual):

| J | K | Q |

|---|---|---|

| 0 | 0 | q |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

Biestable JK activu por lladral

[editar | editar la fonte]

Xunto coles entraes J y K esiste una entrada C de sincronismu o de reló que la so misión ye la de dexar el cambéu d'estáu del biestable cuando se produz un lladral de xubida o de baxada, según sía'l so diseñu. La so denominación n'inglés ye J-K Flip-Flop Edge-Triggered.

Acordies cola tabla de verdá, cuando les entraes J y K tán a nivel lóxicu 1, a cada lladral activu na entrada de reló, la salida del biestable camuda d'estáu. A esta manera de funcionamientu denominar manera de basculación (toggle n'inglés).

Exemplu: 74LS73

Biestable JK Maestru-Esclavu

[editar | editar la fonte]Anque entá puede atopase en dellos equipos, esti tipu de biestable, denomináu n'inglés J-K Flip-Flop Master-Slave, quedó obsoleto yá que foi reemplazáu pol tipu anterior.

El so funcionamientu ye similar al JK activu por lladral: nel nivel altu (o baxu) tómense los valores de les entraes J y K y nel lladral de baxada (o de xubida) reflexar na salida.

Otra forma d'espresar la tabla de verdá del biestable JK ye por aciu la denominada tabla d'escitación:

| J | K | Q | Qsiguiente |

|---|---|---|---|

| 0 | X | 0 | 0

|

| 1 | X | 0 | 1

|

| X | 1 | 1 | 0

|

| X | 0 | 1 | 1

|

| X=nun importa | |||

Siendo Q l'estáu presente y Qsiguiente l'estáu siguiente. La ecuación carauterística del flip flop JK ye: Qsiguiente=JPlantía:Sobrerrayado+Plantía:SobrerrayadoQ la cual llógrase de la tabla carauterística del flip flop.

Exemplu con componentes discretos

[editar | editar la fonte]

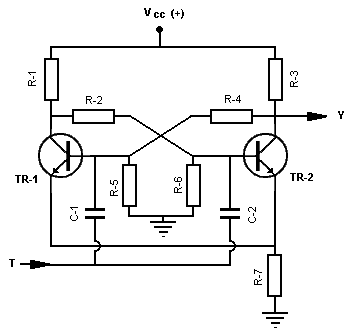

Anque, polo xeneral, los biestables utilizaos na práutica tán implementaos en forma de circuitos integraos, na Figura 1 represéntase l'esquema d'un senciellu circuitu multivibrador biestable, realizáu con componentes discretos, que'l so funcionamientu ye'l siguiente:

Al aplicar la tensión d'alimentación (Vcc), los dos transistores empecipiaren la conducción, yá que les sos bases reciben un potencial positivu, TR-1 al traviés del divisor formáu por R-3, R-4 y R-5 y TR-2 al traviés del formáu por R-1, R-2 y R-6, pero como los transistores nun van ser esautamente idénticos, por el mesmu procesu de fabricación y el grau d'impureces del material semiconductor, unu va conducir antes o más rápidu que l'otru.

Supongamos que ye TR-1 el que conduz primeru. El voltaxe nel so colector va menguar, por cuenta de la mayor cayida de tensión en R-1, polo que la tensión aplicao a la base de TR-2 al traviés del divisor formáu por R-2, R-6, va menguar faciendo qu'esti conduza menos. Esti amenorgamientu de conducción de TR-2 fai que xuba la so tensión de colector y por tanto la de base de TR-1, esti procesu va llevar finalmente al bloquéu de TR-2 (salida Y a nivel altu).

Pero si agora aplicamos un impulsu de disparu de nivel altu pola entrada T, al traviés de los condensadores C-1 y C-2 va pasar a les bases de dambos transistores. Nel casu de TR-1 nun va tener más efeutu qu'aumentar la so tensión positivo, polo qu'esti va siguir conduciendo. Na base de TR-2 l'impulsu va faer qu'esti transistor conduza, realizándose un procesu similar al descritu de primeres, cuando'l que conducía primero yera TR-1, que va terminar bloquiando a este y dexando en conducción a TR-2 (salida Y a nivel baxu).

La secuencia descrita va repitise cada vez que s'aplique un impulsu en T. La salida camuda d'estáu col impulsu de disparu y permanez en dichu estáu hasta la llegada del siguiente impulsu, momentu en que volverá camudar.

La cayida de tensión na resistencia común d'emisores (R-7) esanicia la indecisión del circuitu y aumenta la velocidá de conmutación.

Aplicación

[editar | editar la fonte]Un biestable puede usase p'almacenar un bit. La información contenida en munchos biestables puede representar l'estáu d'un secuenciador, el valor d'un contador, un calter ASCII na memoria d'un ordenador, o cualesquier otra clase d'información.

Un usu corriente ye'l diseñu de máquines d'estáu finitas electróniques. Los biestables almacenen l'estáu previu de la máquina que s'usa pa calcular el siguiente.

El T ye útil pa cuntar. Una señal repetitiva na entrada de reló fai que'l biestable camude d'estáu per cada transición alto-so si la so entrada T ta a nivel 1. La salida d'un biestable puede conectase a la entrada de reló de la siguiente y asina socesivamente. La salida final del conxuntu consideráu como una cadena de salíes de tolos biestables ye'l conteo en códigu binariu del númberu de ciclos na primer entrada de reló hasta un máximu de 2n-1, onde n ye'l númberu de biestables usaos.

Unu de los problemes con esta configuración de contador (ripple counter n'inglés) ye que la salida ye momentáneamente inválida mientres los cambeos arrobinar pola cadena xusto dempués d'un lladral de reló. Hai dos soluciones a esti problema. La primera, ye muestrear la salida namái cuando se sabe que ye válida. La segunda, más complexa y llargamente usada, ye utilizar un tipu distintu de contador síncrono, que tien una lóxica más complexa p'asegurar que toles salíes camuden nel mesmu momentu predeterminado, anque'l preciu a pagar ye l'amenorgamientu de la frecuencia máxima a la que puede funcionar.

Una cadena de biestables T como la descrita enantes tamién sirve pa la división de la frecuencia d'entrada ente 2n, onde n ye'l númberu de biestables ente la entrada y l'última salida.

Secuenciación y metaestabilidad

[editar | editar la fonte]Los biestables síncronos son propensos a sufrir un problema denomináu metaestabilidad, qu'asocede cuando una entrada de datos o de control ta camudando nel momentu en que llega un lladral de reló. La resultancia ye que la salida puede portase de forma imprevista, tardando munches vegaes más de lo normal n'estabilizase al estáu correutu, o inclusive podría bazcuyar repitíes vegaes hasta terminar nel so estáu estable. Nun ordenador esto puede suponer la corrupción de datos o causar un fallu de programa.

En munchos casos, la metaestabilidad nos biestables puede evitase asegurándose de que los datos y les entraes de control caltienen constantes mientres un periodu de tiempu especificáu antes y dempués del lladral de reló, denominaos setup time (tel so) y hold time (th) respeutivamente. Esos tiempos tán establecíos na fueya de datos del dispositivu en cuestión, y son típicamente ente unos pocos nanosegundos y unos pocos cientos de picosegundos pa dispositivos modernos.

Desafortunadamente, non siempres ye posible cumplir estos requisitos, porque los biestables pueden tar coneutaos a entraes en tiempu real que son asíncronas, y pueden camudar en cualquier momentu fuera del control del diseñador. Nesti casu, lo únicu que puede faer se ye amenorgar la probabilidá d'error a un determináu nivel, dependiendo de la fiabilidá que se deseye del circuitu. Una téunica p'amenorgar la incidencia ye coneutar dos o más biestables en cadena, de forma que la salida d'una conéctase a la entrada de la siguiente, y con tolos dispositivos compartiendo la mesma señal de reló. D'esta forma la probabilidá d'un sucesu metaestable puede amenorgase considerablemente, pero nunca va poder esaniciase por completu.

Esisten biestables robustos frente a la metaestabilidad, que funcionen amenorgando los tiempos de setup y hold en tolo posible, pero inclusive estos nun pueden esaniciar por completu'l problema. Esto ye por cuenta de que la metaestabilidad ye muncho más qu'un problema de diseñu. Cuando'l lladral de reló y la entrada de datos tán abondo xuntos, el biestable tien qu'escoyer l'eventu qu'asocedió antes. Y por más rápidu que se faiga'l dispositivu, siempres esiste la posibilidá de qu'asocedan lo suficientemente xuntos como por que non pueda detectase cual ye'l qu'asocedió primero. Con éses ye lóxicamente imposible'l construyir un biestable a prueba de metaestabilidad.

Otru parámetru temporal importante d'un biestable ye'l retardo reló-a-salida (clock-to-output tCO) o retardo d'espardimientu (propagation delay tP), que ye'l tiempu que'l biestable tarda en camudar la so salida tres un lladral de reló. El tiempu pa una transición alto-a-baxu (tPHL) ye dacuando distintu del de les transiciones de baxu-a-altu (tPLH).

Cuando se conecten biestables en cadena, ye importante asegurar que'l tCO del primeru ye mayor que'l hold time (tH) del siguiente, yá qu'en casu contrariu, el segundu biestable nun va recibir los datos de forma fiable. La rellación ente tCO y tH ta garantizada de normal si ambos biestables son del mesmu tipu.

Ver tamién

[editar | editar la fonte]- Astable

- Latch

- Metaestabilidad

- Microprocesador

- Multivibrador

- Monoestable

- Sesgu de reló

- Condición de carrera

Referencies

[editar | editar la fonte]- ↑ Steven H. Strogatz (2001). Nonlinear Dynamics and Chaos. Westview Press. ISBN 9780738204536.